-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

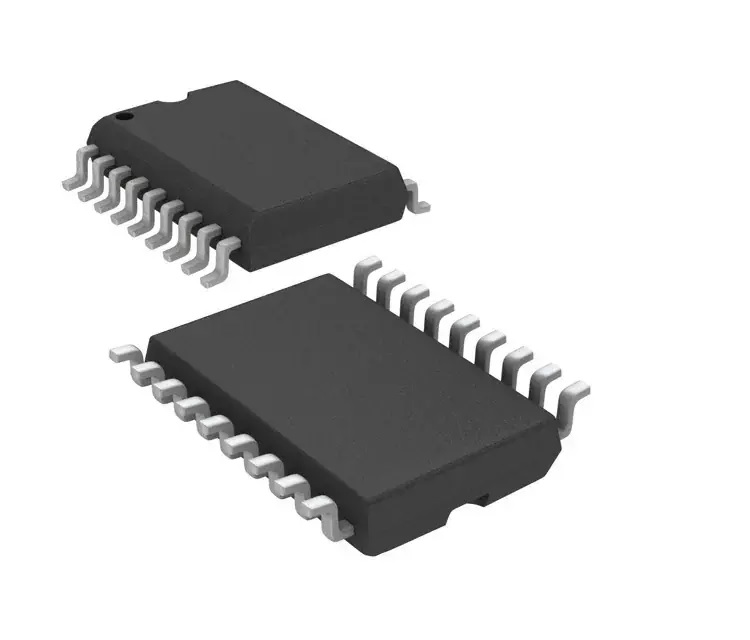

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

- Floor Heating Systems & Parts

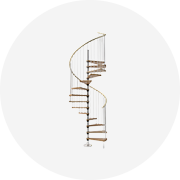

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

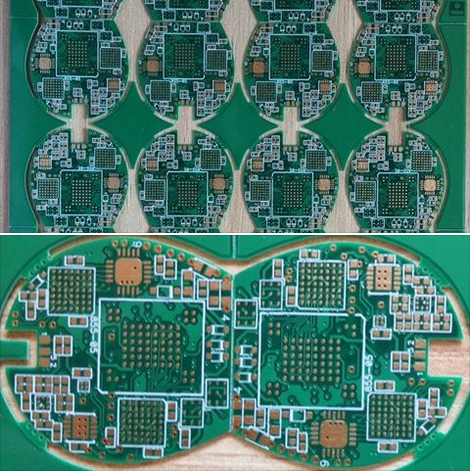

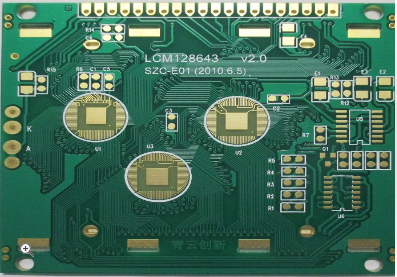

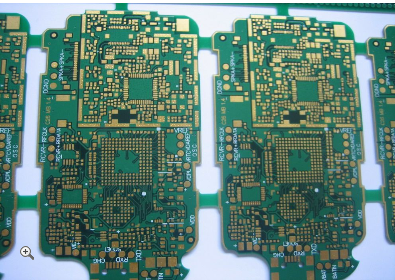

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

Advanced Electronics Layout Design For High Speed Circuit Board Applications

In the rapidly evolving landscape of modern electronics, the demand for higher data rates, greater bandwidth, and enhanced performance has pushed circuit design into the realm of high-speed signals. This is where the specialized discipline of "Advanced Electronics Layout Design for High-Speed Circuit Board Applications" becomes not just relevant, but absolutely critical. It moves far beyond the basic connectivity of traditional PCB layout, entering a domain where every trace, via, and component placement is a calculated decision to preserve signal integrity, manage electromagnetic interference, and ensure reliable operation at gigahertz frequencies. From cutting-edge telecommunications infrastructure and high-performance computing servers to advanced automotive radar and medical imaging systems, the principles of advanced high-speed layout are the invisible backbone enabling technological breakthroughs. This article delves into the core aspects of this sophisticated field, exploring the fundamental challenges and methodologies that define successful high-speed PCB implementation.

Signal Integrity: The Paramount Consideration

At the heart of high-speed design lies the imperative of maintaining signal integrity (SI). As signal edge rates become incredibly fast—often in the picosecond range—traces on the board no longer behave as simple wires but as transmission lines. When the electrical length of a trace approaches a significant fraction of the signal's wavelength, effects like reflection, crosstalk, and attenuation dominate. A primary tool for controlling these effects is impedance matching. Designers must meticulously calculate and control the characteristic impedance of traces (commonly 50 or 100 ohms for differential pairs) through precise management of trace width, dielectric material thickness, and copper weight. A mismatch in impedance causes signal reflections, leading to overshoot, undershoot, and data errors at the receiver.

Furthermore, managing signal paths for critical nets, such as clocks and high-speed data buses, requires strict length matching and topology control. Designers employ techniques like serpentine routing to add deliberate delay, ensuring that related signals arrive simultaneously at their destination. The choice of routing strategy—whether point-to-point, daisy-chain, or fly-by—is dictated by the specific protocol (e.g., DDR memory, PCI Express). Neglecting these SI principles results in a board that may power on but will fail under operational conditions, with intermittent glitches and corrupted data that are notoriously difficult to diagnose.

Power Integrity and Advanced Power Distribution Network (PDN) Design

A stable and clean power supply is the foundation upon which signal integrity is built. In high-speed circuits, the Power Distribution Network (PDN) is a dynamic, frequency-dependent system. The primary challenge is to provide a low-impedance path for current from the power source to every integrated circuit across a broad frequency range, from DC up to several gigahertz. Transient switching currents from modern processors and FPGAs can be massive and rapid, causing voltage droops or ground bounce if the PDN is inadequate. This directly impacts noise margins and can cause false switching.

To achieve this, advanced layout employs a multi-layered strategy. This includes the use of dedicated power and ground planes in a multilayer stack-up to provide inherent capacitance and low inductance. Strategic placement of decoupling capacitors is crucial: bulk capacitors handle lower frequency demands, while a hierarchy of smaller, low-inductance ceramic capacitors are placed as close as possible to device power pins to suppress high-frequency noise. The design of the PDN is often supported by sophisticated simulation tools that model the impedance profile (Z11) to identify resonant frequencies and ensure the impedance stays below the target threshold across the required bandwidth.

Electromagnetic Compatibility (EMC) and Controlled Impedance Routing

High-speed designs must not only function internally but also comply with stringent electromagnetic compatibility (EMC) regulations, limiting both emissions and susceptibility. A poorly laid-out high-speed board can act as an efficient antenna, radiating noise and causing interference with other devices, or failing immunity tests. Controlled impedance routing, as mentioned for SI, is equally vital for EMC. Properly terminated transmission lines minimize ringing and reduce high-frequency harmonic content that leads to radiation.

Layout techniques to enhance EMC include providing uninterrupted ground planes as return paths for high-speed currents, minimizing loop areas by routing signal traces close to their reference plane, and using guard traces or ground shielding for extremely sensitive nets. The placement and filtering of I/O connectors where high-speed signals enter or exit the board are critical zones. Furthermore, the stack-up design itself is a powerful EMC tool. Symmetrical, tightly coupled layer arrangements with buried signal layers between ground planes can effectively contain electromagnetic fields, turning the PCB into a shielded enclosure for its signals.

Material Selection and Stack-up Architecture

The physical construction of the PCB, defined by its materials and layer stack-up, is a fundamental design choice made before a single component is placed. For high-speed applications, standard FR-4 material may not suffice at higher frequencies due to its more lossy nature and less stable dielectric constant (Dk). Advanced laminates with lower dissipation factor (Df) and tightly controlled Dk, such as Rogers, Isola, or specialized Megtron grades, are often employed for critical high-frequency layers to reduce signal attenuation and phase distortion.

The stack-up architecture determines the electrical environment for every trace. A well-planned stack-up assigns dedicated layers for power and ground, ensuring short return paths and defining controlled impedance. It also considers the proximity of signal layers to their reference planes and the order of layers to manage crosstalk between adjacent signal layers. Decisions on copper weight, dielectric thickness, and prepreg material all feed into the impedance calculations and overall thermal and mechanical performance of the assembly. This pre-layout planning phase is arguably one of the most important steps in guaranteeing a successful high-speed design.

Utilization of Advanced Design and Analysis Tools

The complexity of modern high-speed layouts makes reliance on experience and manual calculation insufficient. The field is now driven by a suite of powerful electronic design automation (EDA) tools. These tools integrate schematic capture, layout, and, most importantly, pre-layout and post-layout simulation. SI/PI analysis tools can extract parasitic parameters from the physical layout, simulate eye diagrams to predict data integrity, and analyze power plane resonances.

3D electromagnetic field solvers are used to model complex structures like connectors, vias, and antennas. Furthermore, design rule checking (DRC) has evolved into constraint-driven design, where electrical rules (e.g., length, delay, impedance) are defined upfront and the layout tool actively guides the designer to comply. This iterative process of design, simulate, analyze, and refine is essential for first-pass success, reducing costly board spins and development time in projects where performance margins are razor-thin.

REPORT