-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

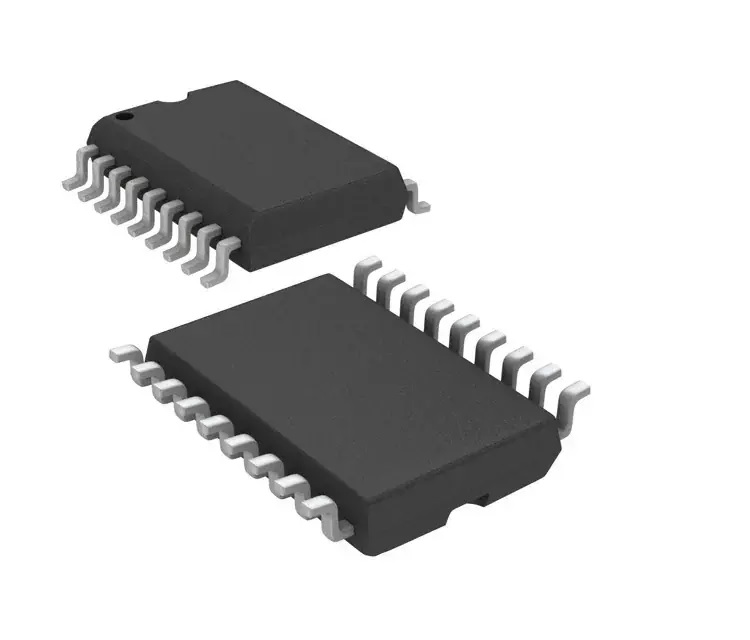

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

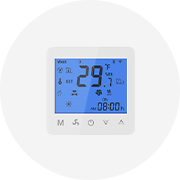

- Floor Heating Systems & Parts

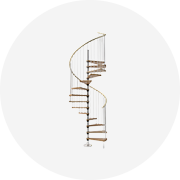

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

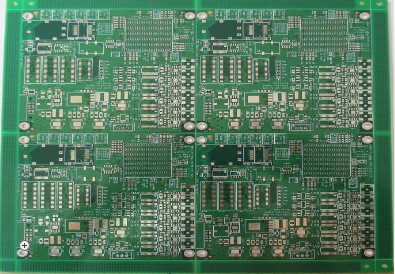

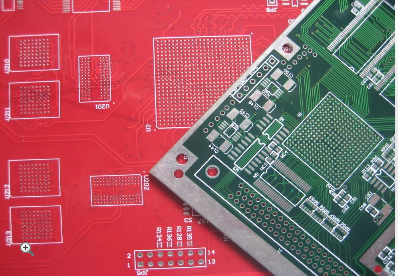

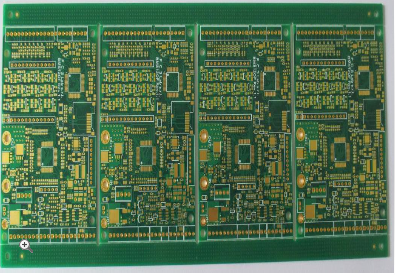

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

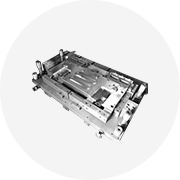

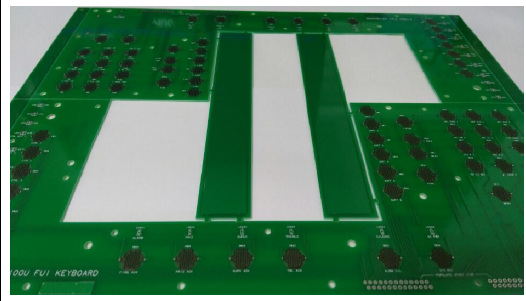

Compact Visualization System PCB Design Integrating High Speed Interfaces and Memory Controller Modules

In the rapidly evolving landscape of electronic systems, the demand for compact, high-performance visualization solutions has surged, driven by applications ranging from medical imaging to autonomous vehicles and immersive gaming. At the heart of these advancements lies the intricate world of printed circuit board (PCB) design, where the integration of high-speed interfaces and memory controller modules plays a pivotal role. The Compact Visualization System PCB Design, which seamlessly incorporates these elements, represents a cutting-edge approach to meeting the challenges of modern data processing and display. This system is not merely a collection of components but a meticulously engineered platform that balances size constraints with the need for lightning-fast data transfer and efficient memory management. By delving into this topic, readers will gain insights into how such designs enable real-time rendering, reduce latency, and support complex graphical workloads, all while maintaining a small form factor. The background of this field stems from the growing reliance on edge computing and IoT devices, where space and power efficiency are paramount. As industries push the boundaries of what's possible, understanding the nuances of this PCB design becomes essential for engineers, designers, and technology enthusiasts alike.

High-Speed Interface Integration

The integration of high-speed interfaces is a cornerstone of the Compact Visualization System PCB Design, enabling rapid data exchange between components. Interfaces such as PCI Express (PCIe), HDMI, and USB 3.0 are commonly employed to handle the massive bandwidth required for high-resolution graphics and video streams. For instance, PCIe Gen4 or Gen5 can support data rates exceeding 16 GT/s per lane, ensuring that visual data flows seamlessly from processors to display units. This is critical in applications like virtual reality, where even minor delays can cause motion sickness or disrupt user immersion. The design must account for signal integrity, minimizing losses and reflections through careful impedance matching and controlled dielectric materials.

Moreover, the implementation of these interfaces involves sophisticated routing techniques to avoid crosstalk and electromagnetic interference (EMI). Differential pair routing, for example, is used to maintain signal integrity over long traces on the PCB. Designers often utilize simulation tools to model signal behavior before fabrication, identifying potential bottlenecks such as skew or jitter. In the Compact Visualization System, space constraints add another layer of complexity, requiring creative layout strategies like embedded components or microvia structures. By optimizing the placement of interface connectors and transceivers, the system achieves a balance between performance and miniaturization, paving the way for next-generation portable devices.

Memory Controller Module Design

Memory controller modules are integral to the Compact Visualization System, as they manage the flow of data between the central processing unit (CPU) or graphics processing unit (GPU) and memory units like DDR4 or DDR5 SDRAM. These controllers ensure that large datasets, such as texture maps and frame buffers, are accessed efficiently to support real-time rendering. In high-performance visualization, memory bandwidth can be a limiting factor; thus, controllers must support high clock speeds and low latency. For example, DDR5 memory offers data rates up to 6400 MT/s, which requires precise timing calibration in the PCB design to prevent data corruption.

The design of these modules also involves power management considerations, as memory operations can consume significant energy in compact systems. Techniques such as dynamic voltage and frequency scaling (DVFS) are implemented to adjust power based on workload demands, extending battery life in mobile applications. Additionally, the physical layout must address signal integrity challenges, like ensuring that address and data lines are length-matched to avoid timing mismatches. Thermal management is another critical aspect, as密集的 memory arrays can generate heat that affects reliability. By incorporating heat sinks or thermal vias, the PCB design mitigates these risks, ensuring stable operation under heavy graphical loads.

Signal Integrity and Power Integrity

Signal integrity (SI) and power integrity (PI) are paramount in the Compact Visualization System PCB Design, directly impacting the reliability of high-speed data transmission and memory operations. SI focuses on preserving the quality of electrical signals as they traverse the PCB, preventing issues like attenuation, distortion, or noise. In systems integrating interfaces like PCIe or HDMI, even minor imperfections can lead to bit errors, degrading visual output. To combat this, designers employ techniques such as termination resistors, ground planes, and controlled impedance routing. For instance, using stripline or microstrip transmission lines helps maintain consistent signal propagation speeds, essential for synchronizing data across multiple lanes.

Power integrity, on the other hand, ensures that the supply voltages remain stable under varying loads, which is crucial for memory controllers and processors that draw fluctuating currents. Decoupling capacitors are strategically placed near power pins to filter noise and provide transient current support, reducing voltage droops that could cause system crashes. In compact designs, the limited board space complicates PI management, necessitating advanced power distribution networks (PDNs) with multiple layers dedicated to power and ground. Simulation tools like SPICE or finite element analysis are used to model PDN performance, identifying resonance points or impedance mismatches early in the design phase. By addressing SI and PI holistically, the Compact Visualization System achieves robust operation, even in demanding environments like automotive displays or industrial control panels.

Thermal Management and Reliability

Thermal management is a critical aspect of the Compact Visualization System PCB Design, as high-speed interfaces and memory controllers generate substantial heat that can compromise performance and longevity. In compact form factors, dissipating this heat efficiently is challenging due to limited airflow and surface area. Designers incorporate thermal vias, which are plated holes that transfer heat from components to inner layers or heat sinks, helping to distribute thermal energy evenly. For example, in a system using a GPU for real-time visualization, copper pours and thermal pads are often integrated into the PCB layout to enhance conduction.

Beyond heat dissipation, reliability considerations include material selection and environmental robustness. High-temperature laminates like FR-4 or polyimide are chosen for their thermal stability, ensuring the PCB withstands repeated heating cycles without delamination or warping. In applications such as outdoor digital signage or medical devices, the design must also account for humidity, vibration, and other stressors. Accelerated life testing is commonly performed to validate the system's durability over time. By prioritizing thermal and reliability factors, the Compact Visualization System maintains consistent performance, reducing the risk of failures that could lead to costly downtime or safety hazards in critical applications.

Miniaturization and Layout Optimization

Miniaturization is a defining feature of the Compact Visualization System PCB Design, driven by the need for portable and space-constrained applications. Achieving a small footprint without sacrificing performance requires innovative layout strategies, such as high-density interconnect (HDI) technology. HDI PCBs use microvias and fine-pitch components to increase routing density, allowing more functions to be packed into a smaller area. This is particularly beneficial for integrating memory modules and high-speed interfaces, as it reduces trace lengths and improves signal timing. For instance, by placing a DDR5 memory controller close to the RAM chips, the design minimizes latency and parasitic effects.

Layout optimization also involves component placement and routing prioritization to avoid congestion and ensure manufacturability. Automated design tools aid in arranging elements to minimize cross-talk and EMI, while adhering to design rules for fabrication and assembly. In many cases, 3D modeling is used to visualize the spatial relationships between components, ensuring that height restrictions are met for enclosures. Additionally, the use of ball grid array (BGA) packages for processors and memory controllers allows for a higher pin count in a compact area, though it demands precise soldering techniques. Through these approaches, the Compact Visualization System achieves a balance of size, cost, and functionality, enabling its deployment in diverse fields from consumer electronics to aerospace.

REPORT