-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

- Floor Heating Systems & Parts

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

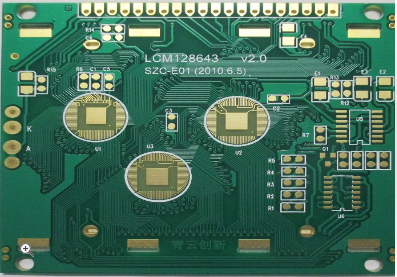

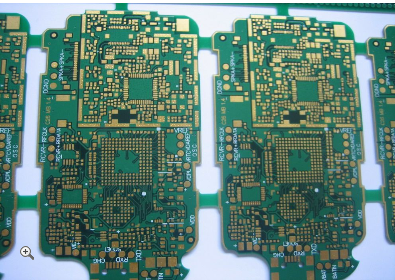

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

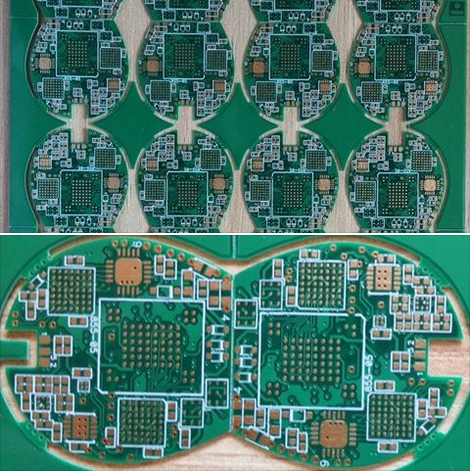

High Performance Line Card PCBs Supporting Data Intensive Applications And Workloads

In today's digital era, the exponential growth of data-intensive applications—from cloud computing and artificial intelligence to 5G networks and the Internet of Things—has placed unprecedented demands on network infrastructure. At the heart of this evolution lies the line card, a critical component in routers and switches that processes and forwards data packets at lightning speeds. High-performance line card printed circuit boards (PCBs) are engineered to meet these rigorous demands, enabling seamless support for massive data workloads. As data volumes surge and latency requirements tighten, the design and capabilities of these PCBs have become a focal point for innovation, driving advancements in speed, reliability, and efficiency. This article delves into the key aspects of these sophisticated PCBs, exploring how they empower modern networks to handle intensive applications without compromise.

Advanced Material Selection for Signal Integrity

The foundation of any high-performance line card PCB lies in the materials used in its construction. Traditional FR-4 substrates, while cost-effective, often fall short in handling the high-frequency signals and thermal management required for data-intensive workloads. Instead, manufacturers turn to advanced laminates like Rogers, Teflon, or ceramic-filled materials, which offer superior dielectric properties and reduced signal loss. These materials minimize attenuation and crosstalk, ensuring that data integrity is maintained even at multi-gigabit per second speeds. For instance, in 400G Ethernet applications, where signal paths can extend across dense layouts, low-loss materials help preserve waveform fidelity, reducing bit error rates and enhancing overall system reliability.

Beyond dielectric performance, thermal management is a critical consideration. High-speed components, such as application-specific integrated circuits (ASICs) and network processors, generate significant heat during operation. Materials with high thermal conductivity, like metal-core PCBs or those infused with thermally conductive fillers, dissipate heat efficiently, preventing overheating that could degrade performance or shorten component lifespan. By integrating these advanced materials, line card PCBs can sustain prolonged operation under heavy loads, making them ideal for data centers and telecom hubs where uptime is paramount.

Multi-Layer Stackup and High-Density Interconnects

To accommodate the complexity of modern networking hardware, high-performance line card PCBs often feature multi-layer stackups, sometimes exceeding 20 layers. This layered approach allows for the segregation of power, ground, and signal planes, which is essential for minimizing electromagnetic interference (EMI) and ensuring stable power delivery. For example, dedicated power planes can provide low-impedance paths to high-current components, reducing voltage drops and noise that might otherwise impair signal quality. Meanwhile, carefully arranged signal layers enable the routing of differential pairs—critical for high-speed interfaces like PCIe or Ethernet—with controlled impedance and minimal skew.

Complementing the stackup is the use of high-density interconnect (HDI) technology, which incorporates microvias, buried vias, and fine-pitch traces to maximize routing density. In data-intensive scenarios, where line cards must support numerous ports and interfaces, HDI design enables tighter component placement and shorter signal paths. This not only reduces propagation delays but also enhances signal integrity by minimizing parasitic effects. As a result, HDI PCBs can integrate more functionality into compact form factors, supporting the scalability needed for evolving network demands without sacrificing performance.

Impedance Control and Signal Integrity Optimization

Maintaining consistent impedance across transmission lines is paramount for high-speed data transmission. Variations in impedance can lead to signal reflections, jitter, and ultimately, data corruption. High-performance line card PCBs employ rigorous impedance control techniques during fabrication, such as precise trace width and spacing calculations, coupled with controlled dielectric thickness. For differential signals commonly used in SerDes (Serializer/Deserializer) architectures, impedance matching ensures that pairs operate symmetrically, canceling out noise and improving noise immunity. Simulation tools, like ANSYS HFSS or Cadence Allegro, are often used to model and validate these parameters before production, reducing the risk of post-deployment issues.

Additionally, signal integrity is further enhanced through careful consideration of return paths, via stubbing, and termination strategies. For instance, the use of ground planes adjacent to signal layers provides low-inductance return paths, minimizing loop areas that could emit EMI. Similarly, back-drilling—a process that removes unused portions of vias—reduces stub effects that can cause resonance and signal degradation at high frequencies. By addressing these nuances, line card PCBs achieve robust performance across a wide frequency spectrum, enabling reliable operation in environments with fluctuating data loads.

Power Integrity and Thermal Management

As line cards handle increasing data throughput, their power requirements escalate, necessitating robust power integrity measures. Voltage regulators, decoupling capacitors, and power distribution networks (PDNs) must work in harmony to deliver stable power to sensitive components. Poor power integrity can manifest as ripple or noise on supply rails, leading to timing errors or component malfunction. To mitigate this, high-performance PCBs incorporate low-ESR (equivalent series resistance) capacitors placed close to power pins, as well as optimized PDN designs that minimize impedance across key frequency ranges. This ensures that even during sudden current spikes—common in bursty data traffic—voltage levels remain within tolerance.

Thermal management goes hand-in-hand with power integrity, as inefficient heat dissipation can exacerbate power-related issues. Beyond material choices, thermal vias, heat sinks, and integrated cooling solutions are employed to channel heat away from hotspots. For example, thermal vias placed under high-power ASICs transfer heat to inner ground planes or external heatsinks, maintaining junction temperatures within safe limits. In advanced applications, liquid cooling or phase-change materials may be integrated directly into the PCB assembly, allowing for sustained performance in densely packed equipment racks. Together, these strategies ensure that line cards remain operational under continuous, high-intensity workloads.

Testing and Validation for Reliability

Before deployment, high-performance line card PCBs undergo rigorous testing to validate their ability to support data-intensive applications. This includes signal integrity tests, such as time-domain reflectometry (TDR) and vector network analyzer (VNA) measurements, to verify impedance consistency and s-parameters. These tests help identify anomalies like impedance mismatches or excessive insertion loss, which could compromise data rates. Additionally, bit error rate (BER) testing simulates real-world traffic patterns, assessing the PCB's performance under stress and ensuring compliance with industry standards, such as IEEE for Ethernet or OIF for optical interfaces.

Environmental and longevity tests further bolster reliability. Thermal cycling, vibration testing, and humidity exposure evaluate the PCB's resilience in harsh operating conditions, common in data centers or outdoor installations. By subjecting prototypes to accelerated aging, manufacturers can predict lifespan and identify potential failure points, leading to design refinements that enhance durability. This comprehensive validation process not only ensures that line card PCBs meet performance benchmarks but also instills confidence in their ability to handle the relentless demands of modern data workloads.

REPORT