-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

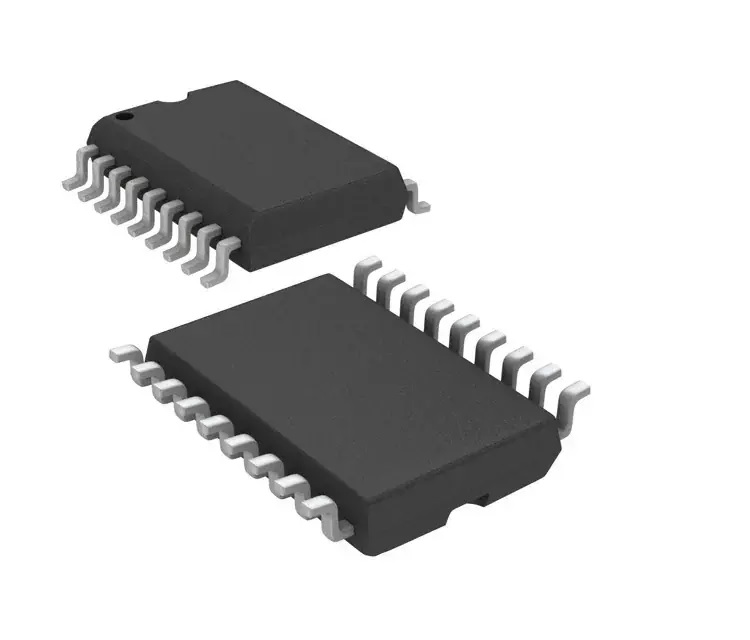

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

- Floor Heating Systems & Parts

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

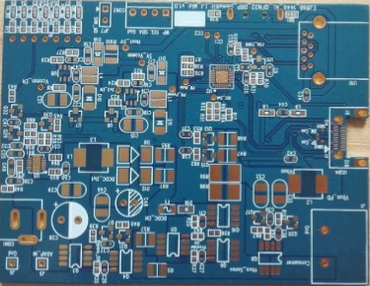

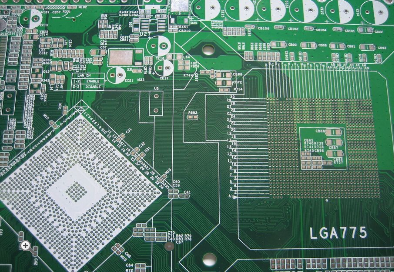

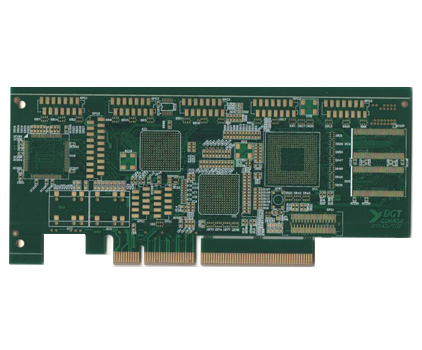

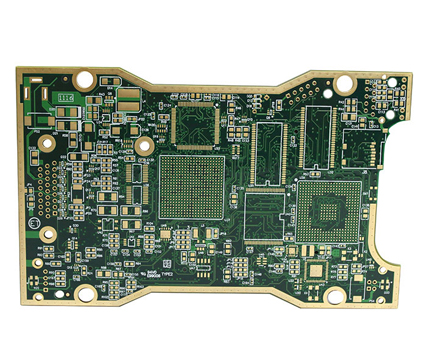

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

Future Trends in PCB Impedance Technology Innovations Driving Precision and Efficiency in Next Generation Electronic Devices

The relentless march of technological progress, fueled by the demands of artificial intelligence, 5G/6G connectivity, and the Internet of Things (IoT), is pushing electronic devices to unprecedented levels of performance and miniaturization. At the heart of this evolution lies the printed circuit board (PCB), the fundamental platform that interconnects all electronic components. While often overlooked, the electrical characteristics of the PCB traces—specifically their impedance—are becoming a critical bottleneck and a primary area for innovation. As signal speeds soar into the multi-gigahertz range and power delivery networks grow more complex, maintaining precise and consistent impedance control is no longer a luxury but an absolute necessity for signal integrity, power integrity, and overall system reliability. This article delves into the future trends in PCB impedance technology, exploring the groundbreaking innovations that are set to drive the precision and efficiency of next-generation electronic devices, from high-performance computing and advanced telecommunications to cutting-edge consumer electronics.

Advanced Materials and Novel Substrates

The foundation of any PCB's electrical performance is its material composition. Traditional FR-4 laminates, while cost-effective, struggle with the dielectric losses and dimensional instability at extremely high frequencies. The future is steering towards advanced materials engineered specifically for superior impedance control. Low-loss, ultra-low-loss, and very-low-loss laminates with tightly controlled dielectric constants (Dk) and dissipation factors (Df) are becoming standard for high-speed digital and RF applications. These materials, often based on specialized hydrocarbon resins or polyphenylene ether (PPE), provide a more stable electrical environment, minimizing signal attenuation and ensuring impedance consistency across the board.

Furthermore, the integration of novel substrate technologies is on the horizon. This includes the increased use of flexible and rigid-flex PCBs with advanced polyimide films that maintain stable impedance under bending stress, crucial for wearable and foldable devices. Another promising area is the development of embedded substrate technologies, where passive components like resistors and capacitors are buried within the PCB layers. This not only saves surface space but also allows for more optimized, shorter, and impedance-controlled interconnection paths, reducing parasitic effects and improving signal quality in dense packaging solutions like System-in-Package (SiP).

AI-Driven Design and Simulation Tools

The complexity of modern PCB designs, with their dense layouts, differential pairs, and intricate power planes, makes manual impedance calculation and routing virtually impossible. The future belongs to artificial intelligence (AI) and machine learning (ML) enhanced electronic design automation (EDA) tools. These next-generation platforms will move beyond traditional rule-based checking to predictive and generative design. AI algorithms can analyze vast datasets of past designs and simulation results to predict potential impedance discontinuities, crosstalk, and resonance issues before the board is ever manufactured.

These intelligent tools will offer real-time impedance guidance during layout, suggesting optimal trace widths, spacing, and layer stack-ups to meet target impedance values automatically. They can perform multi-physics simulations that concurrently analyze signal integrity, power integrity, and thermal effects, understanding how temperature variations might affect the dielectric constant of the material and, consequently, the impedance. This shift from verification to prevention will drastically reduce design cycles, improve first-pass success rates, and enable the creation of highly optimized, high-yield PCB designs that were previously unattainable.

Precision Manufacturing and Process Control

Even the most perfect design can be undermined by manufacturing variances. The trend in PCB fabrication is towards unprecedented levels of precision and process control to achieve the impedance tolerances required for future devices. This involves advancements in several key areas. Laser direct imaging (LDI) and advanced lithography techniques are enabling finer trace definitions and smoother sidewalls, which are essential for controlled impedance at high frequencies, as rough copper edges can increase loss and cause impedance variations.

Similarly, improved etching processes and copper foil technologies, such as very-low-profile (VLP) and reverse-treated foils, provide more consistent conductor geometry. In-situ monitoring and Industry 4.0 practices are being integrated into fabrication lines. Sensors and automated optical inspection (AOI) systems equipped with machine vision can measure critical dimensions like trace width and dielectric thickness in real-time, allowing for immediate process adjustments. This closed-loop, data-driven manufacturing approach ensures that every batch of PCBs consistently meets the stringent impedance specifications, pushing the boundaries of what is manufacturable at scale.

Integration with Advanced Packaging and Heterogeneous Integration

The frontier of electronics is moving beyond the traditional PCB to include advanced packaging schemes. Impedance control is becoming a critical co-design parameter across the entire system hierarchy—from the on-die interconnects and the package substrate to the main PCB. Innovations in fan-out wafer-level packaging (FOWLP), silicon interposers, and 2.5D/3D IC integration require seamless impedance matching between these different domains to prevent signal reflections and losses at the interfaces.

Future trends point towards the holistic design and modeling of "hybrid" boards that incorporate embedded active dies, photonic interconnects, and antenna-in-package (AiP) structures. This heterogeneous integration demands a unified approach to impedance management. Techniques like co-designing the package substrate and motherboard as a single entity, using advanced via technologies (e.g., coaxial vias in substrates) for better impedance continuity through vertical transitions, and integrating optical waveguides for ultra-high-speed data links will all rely on sophisticated impedance control strategies to function as a cohesive, high-performance system.

Impedance Control for Power Integrity and High-Power Applications

While often associated with high-speed signals, impedance technology is equally vital for power delivery networks (PDNs). As processors and ASICs demand higher currents with lower voltages and tighter noise margins, the impedance of the PDN from the voltage regulator module (VRM) to the silicon must be meticulously managed. Future trends involve treating the entire power plane as a controlled impedance structure to minimize parasitic inductance and ensure a stable power supply.

This is leading to innovations in embedded capacitance materials, where very thin dielectric layers with high capacitance density are built into the PCB stack-up very close to the consuming device. These materials act as ultra-localized charge reservoirs, presenting a low-impedance path for high-frequency noise and reducing voltage droop. Furthermore, for high-power applications like electric vehicle inverters or RF power amplifiers, managing the impedance of high-current paths is crucial to minimize losses and thermal buildup. This involves optimized busbar designs, the use of thick copper and special plating, and careful management of return paths, all guided by precise impedance analysis tools tailored for power electronics.

REPORT