-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

- Floor Heating Systems & Parts

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

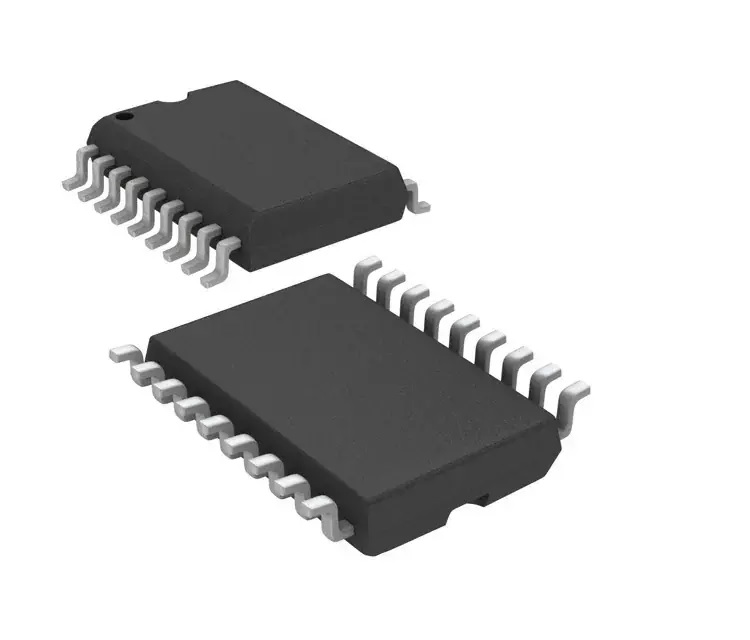

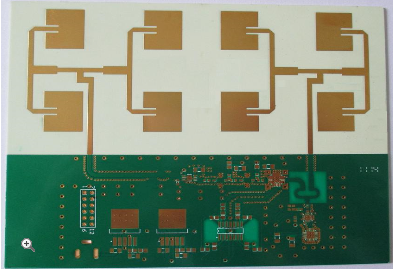

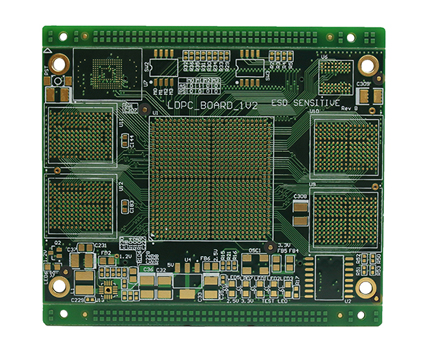

Mastering Impedance Control And Layout Strategies In High Frequency PCB Design To Minimize Signal Loss And Ensure Reliable Circuit Operation

In the rapidly evolving landscape of modern electronics, the demand for higher data rates and faster processing speeds has pushed signal frequencies into the gigahertz range. This shift presents a formidable challenge for printed circuit board (PCB) designers: how to preserve signal integrity across increasingly complex and dense layouts. At the heart of this challenge lies the critical discipline of mastering impedance control and strategic layout design. As frequencies soar, PCBs transition from simple carriers of electrical connections to sophisticated transmission line environments where every trace, via, and plane interaction influences performance. Failure to properly manage these factors leads to signal degradation, reflections, crosstalk, and electromagnetic interference (EMI), ultimately compromising the reliability and functionality of the entire system. This article delves into the essential principles and practical strategies for controlling impedance and optimizing layout in high-frequency PCB design, providing a roadmap to minimize signal loss and ensure robust, dependable circuit operation in applications ranging from telecommunications and networking to advanced computing and radar systems.

The Fundamentals of Controlled Impedance in Transmission Lines

At high frequencies, PCB traces are no longer simple conductive paths but behave as transmission lines. The characteristic impedance of these lines, typically targeted at values like 50Ω or 100Ω for differential pairs, becomes a paramount parameter. It is determined by the physical geometry of the trace and the properties of the surrounding dielectric material. Key factors include the trace width, its thickness (copper weight), the height of the dielectric core or prepreg separating it from the reference plane, and the dielectric constant (Dk or εr) of the laminate material.

Impedance mismatch, where the trace impedance deviates from the source and load impedance, causes signal reflections. These reflections result in standing waves, ringing, and a reduction in the power delivered to the load, manifesting as data errors and timing jitter. Therefore, precise impedance control is not optional but a fundamental requirement. This control begins at the design stage with accurate modeling and calculation using field solvers or industry-standard formulas, and must be meticulously maintained through fabrication, requiring clear communication and tolerancing with the PCB manufacturer.

Strategic Stack-up Design for Signal Integrity

The layer stack-up is the foundational blueprint for impedance control and overall signal integrity. A well-planned stack-up provides clear, uninterrupted reference planes (usually ground or power) adjacent to critical signal layers. These planes serve as the return path for high-frequency signals and are essential for defining a controlled impedance environment. For microstrip traces (on an outer layer), the impedance is primarily controlled by the trace width and the height to the single reference plane beneath. For stripline traces (embedded between two planes), the impedance depends on the trace width and the heights to both the upper and lower planes.

A symmetric stack-up is highly advantageous as it minimizes the risk of board warpage during fabrication and provides balanced mechanical stress. Furthermore, dedicating adjacent layers to orthogonal trace routing (e.g., horizontal on one layer, vertical on the next) with a solid reference plane between them is a classic technique to minimize crosstalk between layers. The choice of laminate material is equally crucial; high-frequency laminates with low and stable dielectric constants and low dissipation factors (Df) are necessary to reduce signal loss and phase distortion at multi-gigahertz frequencies.

Advanced Routing Techniques and Geometries

Once the stack-up is defined, the routing phase implements the impedance control strategy. For single-ended traces, maintaining a consistent width and a constant distance from the reference plane is vital. Any deviation, such as a neck-down or a change in layer without proper management, creates an impedance discontinuity. Corners should be routed with 45-degree angles or curved arcs rather than 90-degree angles, which increase capacitance and cause impedance drops.

For differential pairs, which are ubiquitous in high-speed serial links like PCIe, USB, and Ethernet, the goal is to maintain both the differential impedance (Zdiff) and the common-mode impedance. This requires the two traces of a pair to be routed with identical length, width, and spacing. Length matching, achieved through serpentine tuning sections, is critical to prevent skew and maintain the pair's noise-canceling properties. The spacing between the two traces and the spacing to other signals must be carefully managed to ensure tight coupling within the pair while minimizing crosstalk from adjacent aggressors.

Mitigating Discontinuities: Vias, Transitions, and Terminations

Vias are inevitable in multilayer designs but are significant sources of impedance discontinuities and signal loss at high frequencies. A via acts as a stub, creating parasitic capacitance and inductance that can resonate and cause reflections. Strategies to mitigate via impact include using smaller diameter vias, eliminating unnecessary pad sizes on non-connecting layers (through back-drilling or using blind/buried vias), and ensuring each signal via is placed close to a companion ground via to provide a continuous return path. For the most critical signals, ground return vias should surround the signal via to form a coaxial-like structure.

Proper termination is another key strategy to eliminate reflections at the ends of transmission lines. Series, parallel, or AC termination techniques are used to match the load impedance to the line impedance, absorbing the signal energy and preventing it from reflecting back. The choice of termination depends on the circuit topology and the required power consumption.

Power Integrity and EMI Control as Corollary Objectives

Robust power delivery is inseparable from signal integrity in high-frequency design. Transient currents from switching devices can cause noise on the power distribution network (PDN), which can couple onto sensitive signals. A low-impedance PDN is achieved through the use of strategically placed decoupling capacitors, from bulk to high-frequency ceramic types, and by designing power planes with low inductance. The placement and mounting inductance of these capacitors are as important as their values.

Furthermore, a solid impedance control and layout strategy inherently aids in electromagnetic compatibility (EMC). Controlled impedance paths minimize unintended radiation, while the use of continuous reference planes contains electromagnetic fields. Careful partitioning of analog, digital, and RF sections on the board, along with judicious use of shielding and ground fencing for sensitive circuits, are essential layout strategies to contain EMI and prevent susceptibility to external noise, ensuring the circuit operates reliably in its intended environment.

In conclusion, mastering impedance control and layout strategies is a multifaceted engineering endeavor critical for success in high-frequency PCB design. It requires a deep understanding of electromagnetic principles, meticulous planning from stack-up to routing, and close collaboration with fabrication partners. By treating PCB traces as transmission lines, carefully managing discontinuities, and ensuring power integrity, designers can successfully navigate the challenges of high-speed design, thereby minimizing signal loss and guaranteeing the reliable operation that modern electronic systems demand.

REPORT