-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

- Floor Heating Systems & Parts

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

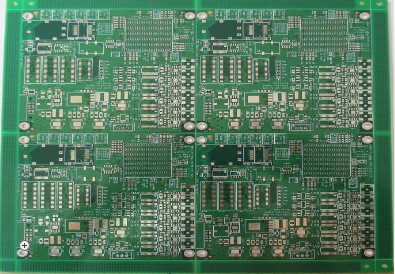

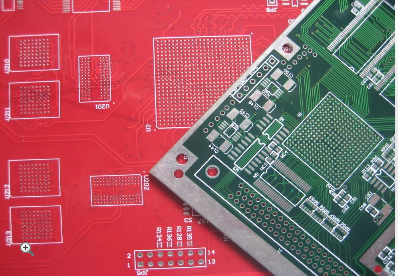

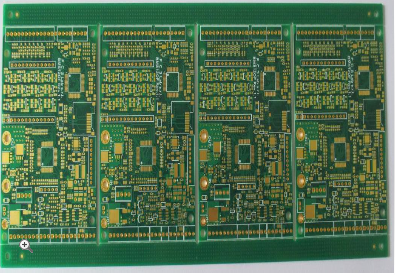

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

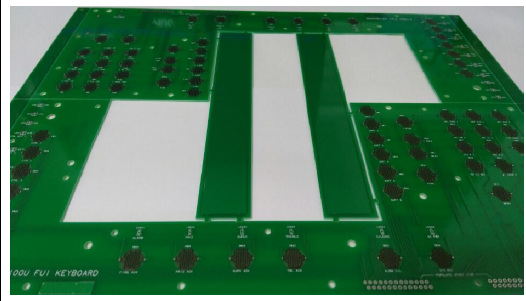

Multilayer PCB Design Strategies For High Speed Server Motherboards With Minimal Electromagnetic Interference

In the rapidly evolving landscape of data centers and cloud computing, the demand for higher processing speeds and greater bandwidth in server motherboards is relentless. This pursuit of performance, however, brings forth a significant engineering challenge: electromagnetic interference (EMI). As signal frequencies climb into the multi-gigahertz range, the printed circuit board (PCB) transforms from a simple interconnect platform into a complex electromagnetic environment where crosstalk, radiated emissions, and signal integrity issues can cripple system reliability. Multilayer PCB design has emerged as the cornerstone technology for taming these high-speed phenomena. By strategically arranging conductive and insulating layers, engineers can create a controlled impedance environment, effectively shielding sensitive signals and distributing power with unprecedented cleanliness. This article delves into the critical multilayer PCB design strategies essential for developing high-speed server motherboards that achieve robust performance while maintaining minimal electromagnetic interference, ensuring compliance with stringent regulatory standards and long-term operational stability.

Strategic Layer Stack-up Configuration

The foundation of any high-speed, low-EMI PCB design is a meticulously planned layer stack-up. For a server motherboard, which may require 12, 16, or even more layers, the arrangement of signal, power, and ground planes is paramount. A symmetrical stack-up is highly recommended to prevent warping during the manufacturing process, but more importantly, it provides a consistent electromagnetic environment. The primary objective is to assign each high-speed signal layer adjacent to a solid reference plane, typically a ground plane.

This adjacency creates a controlled impedance transmission line, such as a microstrip or stripline configuration. Stripline, where a signal layer is embedded between two reference planes, offers superior shielding and lower radiation compared to microstrip, making it ideal for the most critical and noisy signals like PCI Express or DDR memory buses. Furthermore, the stack-up should dedicate entire layers to power distribution. By sandwiching these power planes between ground planes, a distributed decoupling capacitance is formed, which is highly effective at suppressing high-frequency noise on the power rails. This strategic layer pairing is the first and most crucial step in containing electromagnetic fields within the board structure.

Impedance Control and Signal Integrity Management

Maintaining consistent characteristic impedance across all high-speed interconnects is non-negotiable for signal integrity. Impedance discontinuities cause signal reflections, leading to data errors, timing jitter, and increased EMI. The multilayer stack-up allows for precise control over impedance by defining the trace width, the dielectric thickness to the reference plane, and the dielectric constant of the PCB material.

For signals operating above a few gigabits per second, every element of the path must be considered. This includes the vias used to transition between layers. Via stubs—the unused portion of a via—act as resonant antennas, significantly degrading signal quality at high frequencies. Techniques like back-drilling (controlled depth drilling) to remove these stubs are essential for interfaces like SAS/SATA and 10GbE. Additionally, differential signaling, used extensively in high-speed serial links, provides inherent noise immunity. To maximize its benefits, differential pairs must be routed with strict symmetry—maintaining equal trace lengths and consistent spacing between the pair and to other signals—to ensure common-mode noise rejection works effectively.

Power Integrity and Advanced Decoupling Strategies

Power integrity is inextricably linked to signal integrity and EMI performance. A noisy power distribution network (PDN) directly modulates onto signals, causing jitter and radiating noise. The multilayer approach is vital for creating a low-impedance PDN from DC to very high frequencies. The inherent plane capacitance between adjacent power and ground layers provides excellent high-frequency decoupling, but this must be supplemented with a strategic placement of discrete decoupling capacitors.

A multi-tiered decoupling strategy is employed. Bulk capacitors handle lower frequency fluctuations, while smaller ceramic capacitors target mid-range frequencies. However, the parasitic inductance of the capacitor pads and vias limits their effectiveness beyond a few hundred megahertz. This is where the power-ground plane capacitance truly shines, acting as an ideal, distributed capacitor with negligible inductance. To further minimize loop areas—a key antenna for EMI—decoupling capacitors should be placed as close as possible to the power pins of active devices, using short, wide traces and multiple vias to connect to the planes. Power island segmentation for different voltage domains (e.g., CPU core, I/O) with careful consideration of return current paths is also critical to prevent noise coupling between subsystems.

Effective Grounding and Shielding Techniques

A robust and continuous grounding strategy is the shield against EMI. The primary goal is to provide the shortest possible return path for high-frequency currents. When a signal travels on a trace, its return current flows in the reference plane directly beneath it. If this path is interrupted by a split or a gap in the plane, the return current is forced to take a longer, loopier path, dramatically increasing radiation. Therefore, ground planes must be kept as solid as possible, especially underneath high-speed traces.

For areas requiring isolation, such as between analog and digital sections or around crystal oscillators, the use of "moats" or splits must be handled with extreme care. Often, a single, unified ground plane with careful component placement and routing separation is more effective than splitting the plane. Additionally, strategic use of grounded copper pours on signal layers and a "stitching" pattern of vias connecting all ground planes around the perimeter of the board and between sensitive components creates a Faraday cage effect. This via fencing helps contain electromagnetic energy and prevents it from propagating as surface waves or radiating from the edges of the PCB, effectively acting as a built-in shield.

Component Placement and Routing Discipline

The physical layout of components and traces has a profound impact on EMI. The fundamental principle is to minimize the area of current loops, as a large loop area acts as an efficient magnetic antenna. This begins with component placement. High-speed devices like CPUs, memory chips, and switch ICs should be positioned to minimize the length of critical interconnects. Clock generators and oscillators, being potent sources of EMI, should be located centrally to their loads and immediately surrounded by a guard ring of grounding vias.

During routing, critical high-speed signals must be given priority. They should be routed on the inner layers adjacent to solid reference planes to benefit from inherent shielding. A 20H rule—where the power plane is recessed from the edge of the ground plane by a distance of 20 times the dielectric thickness—can be applied to further reduce edge radiation. Furthermore, avoiding sharp 90-degree bends, which can cause impedance changes and act as radiation points, is standard practice; 45-degree angles or curved traces are preferred. Finally, adhering to the 3W rule (spacing traces at least three times the width of a trace from center to center) for parallel runs helps to minimize crosstalk between signals, preserving signal integrity and reducing overall noise.

REPORT