-

Agriculture

Agriculture

-

Health-Care

Health-Care

-

Environment

Environment

-

Construction-Real-Estate

Construction-Real-Estate

-

Tools-Hardware

Tools-Hardware

-

Home-Garden

Home-Garden

-

Furniture

Furniture

-

Luggage-Bags-Cases

Luggage-Bags-Cases

-

Medical-devices-Supplies

Medical-devices-Supplies

-

Gifts-Crafts

Gifts-Crafts

-

Sports-Entertainment

Sports-Entertainment

-

Food-Beverage

Food-Beverage

-

Vehicles-Transportation

Vehicles-Transportation

-

Power-Transmission

Power-Transmission

-

Material-Handling

Material-Handling

-

Renewable-Energy

Renewable-Energy

-

Safety

Safety

-

Testing-Instrument-Equipment

Testing-Instrument-Equipment

-

Construction-Building-Machinery

Construction-Building-Machinery

-

Pet-Supplies

Pet-Supplies

-

Personal-Care-Household-Cleaning

Personal-Care-Household-Cleaning

-

Vehicle-Accessories-Electronics-Tools

Vehicle-Accessories-Electronics-Tools

-

School-Office-Supplies

School-Office-Supplies

-

Packaging-Printing

Packaging-Printing

-

Mother-Kids-Toys

Mother-Kids-Toys

-

Business-Services

Business-Services

-

Commercial-Equipment-Machinery

Commercial-Equipment-Machinery

-

Apparel-Accessories

Apparel-Accessories

-

Security

Security

-

Shoes-Accessories

Shoes-Accessories

-

Vehicle-Parts-Accessories

Vehicle-Parts-Accessories

-

Jewelry-Eyewear-Watches-Accessories

Jewelry-Eyewear-Watches-Accessories

-

Lights-Lighting

Lights-Lighting

-

Fabric-Textile-Raw-Material

Fabric-Textile-Raw-Material

-

Fabrication-Services

Fabrication-Services

-

Industrial-Machinery

Industrial-Machinery

-

Consumer-Electronics

Consumer-Electronics

-

Electrical-Equipment-Supplies

Electrical-Equipment-Supplies

-

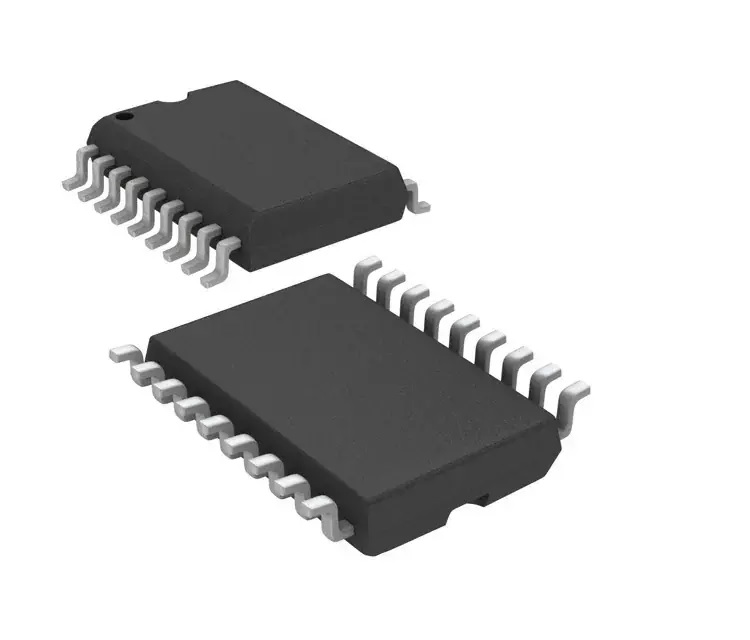

Electronic-Components-Accessories-Telecommunications

Electronic-Components-Accessories-Telecommunications

-

Home-Appliances

Home-Appliances

-

Beauty

Beauty

-

Chemicals

Chemicals

-

Rubber-Plastics

Rubber-Plastics

-

Metals-Alloys

Metals-Alloys

- Masonry Materials

- Curtain Walls & Accessories

- Earthwork Products

- Fireproofing Materials

- Heat Insulation Materials

- Plastic Building Materials

- Building Boards

- Soundproofing Materials

- Timber

- Waterproofing Materials

- Balustrades & Handrails

- Bathroom & Kitchen

- Flooring & Accessories

- Tiles & Accessories

- Door, Window & Accessories

- Fireplaces & Stoves

- Floor Heating Systems & Parts

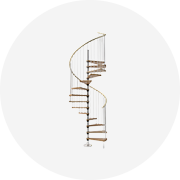

- Stairs & Stair Parts

- Ceilings

- Elevators & Escalators

- Stone

- Countertops, Vanity Tops & Table Tops

- Mosaics

- Metal Building Materials

- Multifunctional Materials

- Ladders & Scaffoldings

- Mouldings

- Corner Guards

- Decorative Films

- Formwork

- Building & Industrial Glass

- Other Construction & Real Estate

- Wallpapers/Wall panels

- HVAC System & Parts

- Outdoor Facilities

- Prefabricated Buildings

- Festive & Party Supplies

- Bathroom Products

- Household Sundries

- Rain Gear

- Garden Supplies

- Household Cleaning Tools & Accessories

- Lighters & Smoking Accessories

- Home Storage & Organization

- Household Scales

- Smart Home Improvement

- Home Textiles

- Kitchenware

- Drinkware & Accessories

- Dinnerware, Coffee & Wine

- Home Decor

- Golf

- Fitness & Body Building

- Amusement Park Facilities

- Billiards, Board Game,Coin Operated Games

- Musical Instruments

- Outdoor Affordable Luxury Sports

- Camping & Hiking

- Fishing

- Sports Safety&Rehabilitation

- Ball Sports Equipments

- Water Sports

- Winter Sports

- Luxury Travel Equipments

- Sports Shoes, Bags & Accessories

- Cycling

- Other Sports & Entertainment Products

- Artificial Grass&Sports Flooring&Sports Court Equipment

- Scooters

- Food Ingredients

- Honey & Honey Products

- Snacks

- Nuts & Kernels

- Seafood

- Plant & Animal Oil

- Beverages

- Fruit & Vegetable Products

- Frog & Escargot

- Bean Products

- Egg Products

- Dairy Products

- Seasonings & Condiments

- Canned Food

- Instant Food

- Baked Goods

- Other Food & Beverage

- Meat & Poultry

- Confectionery

- Grain Products

- Feminie Care

- Hair Care & Styling

- Body Care

- Hands & Feet Care

- Hygiene Products

- Men's Grooming

- Laundry Cleaning Supplies

- Travel Size & Gift Sets

- Room Deodorizers

- Other Personal Care Products

- Pest Control Products

- Special Household Cleaning

- Floor Cleaning

- Kitchen & Bathroom Cleaning

- Oral Care

- Bath Supplies

- Yellow Pages

- Correction Supplies

- Office Binding Supplies

- Office Cutting Supplies

- Board Erasers

- Office Adhesives & Tapes

- Education Supplies

- Pencil Cases & Bags

- Notebooks & Writing Pads

- File Folder Accessories

- Calendars

- Writing Accessories

- Commercial Office Supplies

- Pencil Sharpeners

- Pens

- Letter Pad/Paper

- Paper Envelopes

- Desk Organizers

- Pencils

- Markers & Highlighters

- Filing Products

- Art Supplies

- Easels

- Badge Holder & Accessories

- Office Paper

- Printer Supplies

- Book Covers

- Other Office & School Supplies

- Stationery Set

- Boards

- Clipboards

- Stamps

- Drafting Supplies

- Stencils

- Electronic Dictionary

- Books

- Map

- Magazines

- Calculators

- Baby & Toddler Toys

- Educational Toys

- Classic Toys

- Dress Up & Pretend Play

- Toy Vehicle

- Stuffed Animals & Plush Toys

- Outdoor Toys & Structures

- Balloons & Accessories

- Baby Food

- Children's Clothing

- Baby Supplies & Products

- Maternity Clothes

- Kids Shoes

- Baby Care

- Novelty & Gag Toys

- Dolls & Accessories

- Puzzle & Games

- Blocks & Model Building Toys

- Toddler Clothing

- Baby Clothing

- Kids' Luggage & Bags

- Arts, Crafts & DIY Toys

- Action & Toy Figures

- Baby Appliances

- Hobbies & Models

- Remote Control Toys

- Promotional Toys

- Pregnancy & Maternity

- Hygiene Products

- Kid's Textile&Bedding

- Novelty & Special Use

- Toy Weapons

- Baby Gifts

- Baby Storage & Organization

- Auto Drive Systems

- ATV/UTV Parts & Accessories

- Marine Parts & Accessories

- Other Auto Parts

- Trailer Parts & Accessories

- Auto Transmission Systems

- Train Parts & Accessories

- Universal Parts

- Railway Parts & Accessories

- Auto Brake Systems

- Aviation Parts & Accessories

- Truck Parts & Accessories

- Auto Suspension Systems

- Auto Lighting Systems

- New Energy Vehicle Parts & Accessories

- Auto Steering Systems

- Wheels, Tires & Accessories

- Bus Parts & Accessories

- Auto Performance Parts

- Cooling System

- Go-Kart & Kart Racer Parts & Accessories

- Air Conditioning Systems

- Heavy Duty Vehicle Parts & Accessories

- Auto Electrical Systems

- Auto Body Systems

- Auto Engine Systems

- Container Parts & Accessories

- Motorcycle Parts & Accessories

- Refrigeration & Heat Exchange Equipment

- Machine Tool Equipment

- Food & Beverage Machinery

- Agricultural Machinery & Equipment

- Apparel & Textile Machinery

- Chemical Machinery

- Packaging Machines

- Paper Production Machinery

- Plastic & Rubber Processing Machinery

- Industrial Robots

- Electronic Products Machinery

- Metal & Metallurgy Machinery

- Woodworking Machinery

- Home Product Manufacturing Machinery

- Machinery Accessories

- Environmental Machinery

- Machinery Service

- Electrical Equipment Manufacturing Machinery

- Industrial Compressors & Parts

- Tobacco & Cigarette Machinery

- Production Line

- Used Industrial Machinery

- Electronics Production Machinery

- Other Machinery & Industrial Equipment

- Camera, Photo & Accessories

- Portable Audio, Video & Accessories

- Television, Home Audio, Video & Accessories

- Video Games & Accessories

- Mobile Phone & Accessories

- Electronic Publications

- Earphone & Headphone & Accessories

- Speakers & Accessories

- Smart Electronics

- TV Receivers & Accessories

- Mobile Phone & Computer Repair Parts

- Chargers, Batteries & Power Supplies

- Used Electronics

- VR, AR, MR Hardware & Software

- Projectors & Presentation Equipments

- Other Consumer Electronics

- Cables & Commonly Used Accessories

- Computer Hardware & Software

- Displays, Signage and Optoelectronics

- Discrete Semiconductors

- Wireless & IoT Module and Products

- Telecommunications

- Connectors, Terminals & Accessories

- Development Boards, Electronic Modules and Kits

- Circuit Protection

- Sensors

- Isolators

- Audio Components and Products

- Integrated Circuits

- Power Supplies

- Relays

- RF, Microwave and RFID

- Electronic Accessories & Supplies

- Passive Components

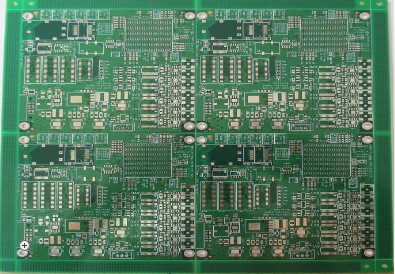

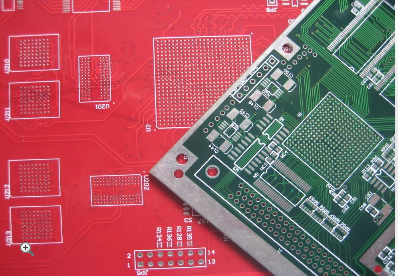

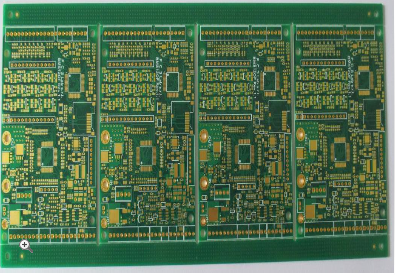

- PCB & PCBA

- Air Quality Appliances

- Home Appliance Parts

- Heating & Cooling Appliances

- Small Kitchen Appliances

- Laundry Appliances

- Water Heaters

- Water Treatment Appliances

- Refrigerators & Freezers

- Personal Care & Beauty Appliances

- Major Kitchen Appliances

- Cleaning Appliances

- Second-hand Appliances

- Smart Home Appliances

- Other Home Appliances

- Energy Chemicals

- Inorganic Chemicals

- Basic Organic Chemicals

- Agrochemicals

- Admixture & Additives

- Catalysts & Chemical Auxiliary Agents

- Pigments & Dyestuff

- Coating & Paint

- Daily Chemicals

- Polymer

- Organic Intermediate

- Adhesives & Sealants

- Chemical Waste

- Biological Chemical Products

- Surface Treatment Chemicals

- Painting & Coating

- Chemical Reagents

- Flavor & Fragrance

- Non-Explosive Demolition Agents

- Other Chemicals

- Custom Chemical Services

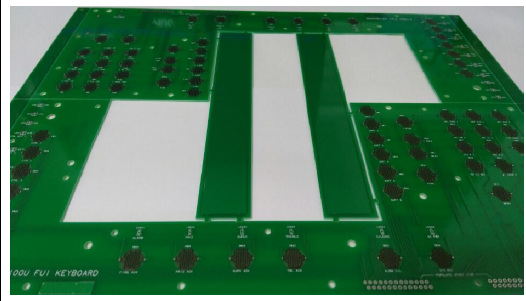

Optimizing Server Motherboard Performance With Precision Engineered Multilayer PCB Layouts And Materials

In the high-stakes world of data centers and enterprise computing, server performance is the bedrock of modern digital infrastructure. At the heart of every powerful server lies its motherboard, a complex ecosystem where the central processing unit (CPU), memory, and peripheral components communicate at breathtaking speeds. However, achieving peak performance is not solely a function of selecting the fastest silicon. The true enabler, often operating behind the scenes, is the precision engineering of the motherboard's printed circuit board (PCB). The intricate dance of electrical signals across this board is what ultimately dictates stability, speed, and efficiency. This article delves into the critical discipline of optimizing server motherboard performance through meticulously designed multilayer PCB layouts and the strategic selection of advanced materials, a field where electrical engineering meets high art to push the boundaries of computational power.

The Critical Role of Multilayer Stack-up Design

The foundation of a high-performance server motherboard is its multilayer stack-up. Unlike simple consumer-grade boards, server PCBs can comprise 12, 16, or even more layers of copper and dielectric material laminated together. This complex sandwich is not arbitrary; it is a carefully orchestrated plan to manage signal integrity, power delivery, and electromagnetic interference (EMI). Each layer is assigned a specific purpose, such as dedicated signal layers, power planes, and ground planes. The arrangement of these layers relative to one another is paramount for controlling impedance and providing stable reference planes for high-speed signals.

Furthermore, the stack-up design directly influences the board's ability to dissipate heat. Server components generate significant thermal energy, and the PCB itself acts as a heat spreader. By incorporating thick copper planes for power distribution, designers can not only reduce resistive losses (IR drop) but also help conduct heat away from hot components like the CPU and voltage regulator modules (VRMs). A poorly designed stack-up can lead to signal degradation, power instability, and thermal throttling, crippling the server's potential. Thus, the initial architectural decision of how to stack the layers sets the stage for all subsequent performance optimizations.

Advanced Materials for High-Speed and Thermal Management

While standard FR-4 material suffices for many applications, the demanding environment of a server motherboard necessitates the use of advanced PCB substrates. Materials with a lower dielectric constant (Dk) and lower dissipation factor (Df) are essential for maintaining signal integrity at multi-gigabit data rates. As signal frequencies increase into the GHz range, standard materials can cause excessive signal attenuation and distortion. High-speed materials, such as those reinforced with specialized glass weaves or ceramic-filled resins, minimize these losses, ensuring that data packets arrive intact and on time.

Thermal performance is another critical driver for material selection. Server motherboards must operate reliably 24/7 under heavy load, making thermal management a top priority. Advanced materials with higher Thermal Decomposition Temperature (Td) and superior Thermal Conductivity are employed to withstand the intense heat. Some high-end designs even incorporate metal cores or heavy copper layers (e.g., 4 oz. copper instead of the standard 1 oz.) within the PCB structure to act as integrated heat sinks, drawing heat away from critical components and improving overall system longevity and stability. The choice of material is a direct trade-off between performance, reliability, and cost, with server applications justifying the investment in premium substrates.

Precision Signal Integrity and Power Integrity Engineering

Signal Integrity (SI) is the discipline of ensuring that electrical signals are not distorted as they travel across the PCB. In a server motherboard, with countless high-speed interfaces like PCI Express, SATA, and memory buses, SI is non-negotiable. Precision layout techniques are employed to manage this. This includes strict control over trace impedance through precise calculation of trace width and distance to reference planes, careful management of trace lengths to meet timing constraints (length matching), and the strategic use of vias to minimize signal reflections. Any imperfection in the signal path can lead to bit errors, data corruption, and system crashes.

Equally important is Power Integrity (PI). A server's CPU and memory can draw hundreds of amps of current with rapid transient demands. The power delivery network (PDN) must provide an exceptionally stable voltage with minimal noise or ripple. This is achieved through a robust combination of multilayer power planes, a dense array of decoupling capacitors placed strategically near power-hungry components, and optimized via patterns to reduce parasitic inductance. A poorly designed PDN can cause voltage droops that force the CPU to reduce its clock speed, directly impacting performance. Therefore, SI and PI are two sides of the same coin, both requiring precise engineering to unlock the full potential of the server hardware.

Mitigating Electromagnetic Interference (EMI)

The high-speed switching of currents in a server motherboard naturally generates electromagnetic interference (EMI). If left unchecked, this EMI can disrupt the operation of the server itself and cause it to fail regulatory compliance tests (like FCC and CE), potentially interfering with other nearby equipment in a data center rack. Precision PCB layout is the first line of defense against EMI. Techniques such as providing uninterrupted ground planes, careful component placement to minimize current loop areas, and the use of shielding cans over noisy circuits are standard practice.

Furthermore, the multilayer stack-up itself is a powerful tool for EMI suppression. By sandwiching high-speed signal layers between solid ground planes, designers create a form of inherent shielding, containing the electromagnetic fields within the board. For the most critical signals, differential signaling (e.g., PCIe, USB) is used, which inherently cancels out emitted noise. For signals that must travel to connectors at the board's edge, EMI filters and careful grounding techniques are employed to prevent the PCB from acting as an antenna. Effective EMI mitigation is not an afterthought but an integral part of the layout process, ensuring the server operates reliably in a dense computing environment.

The Impact of Manufacturing Tolerances and Testing

Even the most perfectly designed PCB layout can be undermined by variations in the manufacturing process. Therefore, designing for manufacturability (DFM) is a crucial aspect of optimization. This involves working within the fabricator's capabilities for minimum trace width and spacing, drill sizes, and layer-to-layer registration. Precision engineering means understanding these tolerances and designing the layout to be robust against them. For instance, specifying controlled impedance requires close collaboration with the PCB manufacturer to ensure the final produced board matches the simulated design.

Rigorous testing validates the precision engineering effort. Once prototypes are built, they undergo extensive automated testing (e.g., flying probe tests) to check for shorts and opens. More importantly, they are subjected to signal integrity validation using vector network analyzers (VNAs) and time-domain reflectometers (TDRs) to measure impedance and S-parameters. Power integrity is tested by measuring voltage ripple under dynamic load. This cycle of simulation, prototyping, and testing is iterative, allowing engineers to refine the layout and material choices until the motherboard meets all performance, reliability, and compliance targets before mass production.

REPORT